**TECHNISCHE FAKULTÄT**

Professur für Höchstleistungsrechnen · Erlangen National High Performance Computing Center

Michael Panzlaff

# **Matrix Power Kernels on GPUs**

# Masterarbeit im Fach Informatik

12. Mai 2024

Please cite as: Michael Panzlaff, "Matrix Power Kernels on GPUs", Master's Thesis, Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Dept. of Computer Science, May 2024.

> Friedrich-Alexander-Universität Erlangen-Nürnberg Department Informatik ProfessurfürHöchstleistungsrechnen Martensstr. 1 · 91058 Erlangen · Germany

# Matrix Power Kernels on GPUs

Masterarbeit im Fach Informatik

vorgelegt von

## **Michael Panzlaff**

geb. am 29. Januar 1996 in Backnang

angefertigt am

# Erlangen National High Performance Computing Center Professur für Höchstleistungsrechnen

Department Informatik Friedrich-Alexander-Universität Erlangen-Nürnberg

| Betreuer:                                | Christie Alappat, M.Sc.<br>Dominik Ernst, M.Sc. |

|------------------------------------------|-------------------------------------------------|

| Betreuender Hochschullehrer:             | Prof. Dr. Gerhard Wellein                       |

| Beginn der Arbeit:<br>Abgabe der Arbeit: | 2. November 2023<br>2. Mai 2024                 |

# Erklärung

Ich versichere, dass ich die Arbeit ohne fremde Hilfe und ohne Benutzung anderer als der angegebenen Quellen angefertigt habe und dass die Arbeit in gleicher oder ähnlicher Form noch keiner anderen Prüfungsbehörde vorgelegen hat und von dieser als Teil einer Prüfungsleistung angenommen wurde. Alle Ausführungen, die wörtlich oder sinngemäß übernommen wurden, sind als solche gekennzeichnet.

# Declaration

I declare that the work is entirely my own and was produced with no assistance from third parties. I certify that the work has not been submitted in the same or any similar form for assessment to any other examining body and all references, direct and indirect, are indicated as such and have been cited accordingly.

(Michael Panzlaff) Erlangen, 12. Mai 2024

# ABSTRACT

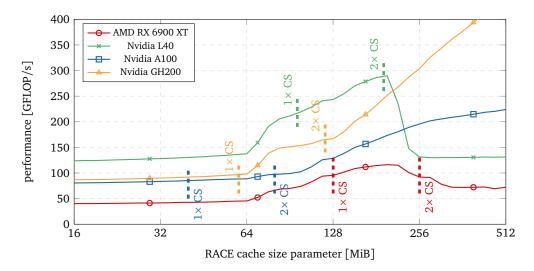

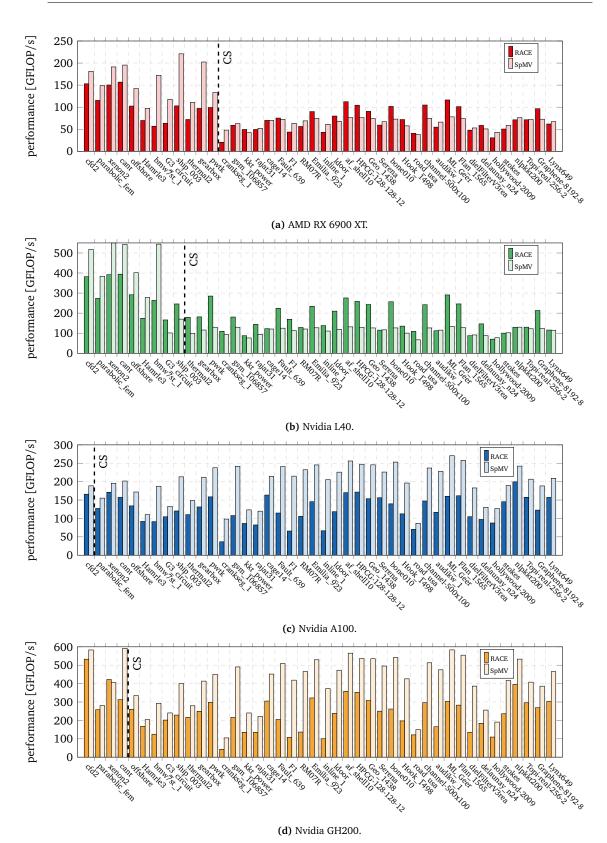

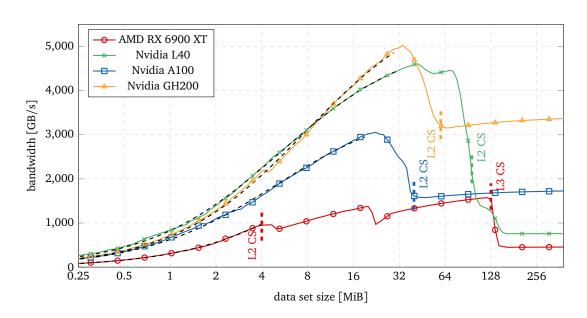

Sparse Matrix-Vector (SpMV) products are used in numerous algorithms of linear algebra and are often the most computationally expensive operation. This includes Krylov Subspace Methods (KSMs) such as GMRES and CG, which rely severely on SpMV to solve linear systems. Since SpMV is known to be very bandwidth intensive, Communication-Avoiding KSMs are an active field of research. They attempt to reduce data interdependencies in the algorithm by replacing expensive SpMV operations with a Matrix Power Kernel (MPK). Doing so allows cache blocking techniques to reuse data from the cache as much as possible in order to reduce the reliance on the limited DRAM bandwidth. However, so far most research has only covered implementations for CPUs. As GPUs are becoming increasingly popular due to their often higher compute and memory performance, we present a benchmark, which runs cache blocked MPKs on GPUs. The benchmark runs on both state-of-the-art Nvidia and AMD GPUs. As a fundamental building block, we use the software library RACE and show that it is possible to get up to a 2× speedup on selected GPUs. Finally, we perform a detailed performance analysis to determine GPU MPK viability for real-world applications. Since a speedup is often not achievable due to kernel call overhead, we predict that MPK performance on future GPUs will heavily depend on their cache size.

# KURZFASSUNG

Dünn besetzte Matrix-Vektor Produkte (SpMV) werden in vielen Algorithmen der linearen Algebra verwendet und sind häufig deren rechenintensivste Operation. Dazu gehören Krylov-Unterraum-Verfahren (KSM) wie GMRES oder CG, welche größtenteils SpMV zum Lösen linearer Gleichungssysteme verwenden. Da SpMV bekanntermaßen sehr bandbreitenintensiv ist, sind kommunikationsvermeidende KSMs ein aktives Forschungsgebiet. Diese versuchen entstehende Datenabhängigkeiten in Algorithmen zu reduzieren, indem SpMV-Operationen durch Matrix-Power-Kernel (MPK) ersetzt werden. Dies erlaubt es, Cache-Blocking-Methoden Daten aus dem Cache so viel wie möglich wiederzuverwenden, damit die begrenzte DRAM-Bandbreite möglichst effizient genutzt wird. Bisher wird jedoch hauptsächlich zu Implementierungen für CPUs geforscht. Da GPUs aufgrund ihrer höheren Rechenleistung und Speicherbandbreite zunehmend verwendet werden, stellen wir einen Benchmark vor, welches mithilfe von Cache-Blocking MPKs auf GPUs berechnet. Dieser Benchmark läuft sowohl auf aktuellen Nvidia als auch AMD GPUs. Die Programmbibliothek RACE wird dafür als grundlegende Komponente verwendet. Wir zeigen auf, dass es damit möglich ist, auf ausgewählten GPUs eine Beschleunigung von 2× zu erreichen. Schlussendlich zeigen wir eine detaillierte Leistungsanalyse um bestimmen zu können, ob MPKs auf GPUs praktikabel sind. Unter anderem wird eine Beschleunigung in vielen Fällen, aufgrund indirekter Kosten, nicht erreicht. Daher prognostizieren wir, dass die MPK-Leistung auf zukünftigen GPUs sehr stark von ihrer Cache Größe abhängen wird.

# CONTENTS

| Ab | stract                                                                                                                                                                                                                                                 | v                                                                                                                            |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Ku | rzfassung                                                                                                                                                                                                                                              | vii                                                                                                                          |

| 1  | Introduction                                                                                                                                                                                                                                           | 1                                                                                                                            |

| 2  | 2.6       HIP Language       1         2.7       GPU Programming Introduction       1                                                                                                                                                                  | <ol> <li>3</li> <li>5</li> <li>7</li> <li>8</li> <li>8</li> <li>8</li> <li>10</li> <li>10</li> <li>10</li> <li>12</li> </ol> |

| 3  | 3.1Benchmarking Goals13.2MPK-HIP13.2.1Benchmark Build Setup13.2.2Dependencies13.2.3Operation Procedure13.2.4Implementation and Optimization13.2.5CRS23.2.6SELL-C- $\sigma$ (naive)23.2.7SELL-C- $\sigma$ (multi threaded)23.2.8HIP Graph23.2.9Summary2 | 17<br>17<br>17<br>18<br>19<br>20<br>22<br>24<br>27<br>28<br>28                                                               |

| 4  | 4.1 Overview and Goals                                                                                                                                                                                                                                 | <b>31</b><br>31                                                                                                              |

#### Contents

|     | 4.3   | gpu-l2    | 2-cache                                 | 3 |

|-----|-------|-----------|-----------------------------------------|---|

|     | 4.4   | MPK-F     | HIP                                     | 5 |

|     |       | 4.4.1     | SpMV Performance                        | 5 |

|     |       |           | 4.4.1.1 Performance Model 33            | 5 |

|     |       |           | 4.4.1.2 Performance Measurements        | 6 |

|     |       |           | 4.4.1.3 In-Cache Performance            | 8 |

|     |       | 4.4.2     | RACE Performance                        | 9 |

|     |       |           | 4.4.2.1 Performance Model 39            | 9 |

|     |       |           | 4.4.2.2 Performance Measurements 44     | 0 |

|     |       |           | 4.4.2.3 Measurement-Based Explanation 4 | 1 |

|     |       |           | 4.4.2.4 Ramp Up Reevaluation 42         | 2 |

|     |       |           | 4.4.2.5 Safety Factor Optimization      |   |

|     |       | 4.4.3     | Final Comparison                        |   |

|     | 4.5   | gpu-sr    | nall-kernels                            | 6 |

| 5   | Con   | clusion   | 49                                      | 9 |

|     | 5.1   | Summ      | nary                                    | 9 |

|     | 5.2   | Future    | e Work                                  | 9 |

| Lis | sts   |           | 5                                       | 1 |

|     | List  | of Acro   | nyms                                    | 1 |

|     |       |           | res5                                    |   |

|     |       |           | es                                      |   |

|     | List  | of Listir | ngs                                     | 7 |

|     | Bibli | ograph    | y                                       | 9 |

|     |       |           |                                         |   |

# INTRODUCTION

Solving linear systems is one of the most essential building blocks in scientific computing and there is continuous research and development to make existing solvers more efficient. For sparse matrices it is well known that most iterative solvers are limited by the Sparse Matrix-Vector (SpMV) operation due to its high memory bandwidth requirement. Today, many algorithms operate on Krylov Subspace Methods (KSMs). These are generally considered to be communication<sup>1</sup> intensive as they typically involve a reduction after each SpMV product.

Alleviating the high memory bandwidth requirements is typically done by better cache utilization due to their much higher bandwidth. However having a high amount of communication in the algorithm means that data often has to be fetched from main memory, because it cannot be reused from cache.

When considering problems which involve matrices being larger than the system's cache, the SpMV operation can only be optimized up to the point where it performs as well as the Dynamic Random Access Memory (DRAM)'s bandwidth allows. In order to make cache reuse possible, the SpMV has to be divided into multiple smaller operations which on their own can reuse the data from the cache independently. This type of strategy is also referred to as *cache blocking* as data is processed in smaller blocks and retained as much in cache as possible. However, due to required communication in the solver's algorithm this becomes impossible without making fundamental changes to it.

One of the key elements the authors of [25] use in order to reduce communication and to speed up computation is the use of Matrix Power Kernels (MPKs), which aim to replace the SpMV in the algorithm. These MPKs calculate the span vectors of the Krylov subspace  $[x, Ax, A^2x, \dots, A^kx]$  with the goal to reduce the reduction after each SpMV to a single reduction after each MPK. Of course doing this does not eliminate the communication entirely, as an SpMV in the general sense forms dependencies between its input and output vectors' rows. Since typical matrices are not entirely random the required communication keeps a limited scope and cache blocking can be utilized. An example for that is "CA-GMRES" [25, Sec. 4], an adaption of GMRES, which uses MPKs instead of SpMV. The authors demonstrate that MPKs can be used in algorithms to get speedup of more than a factor of two.

Regardless of whether a linear system solver or Eigenvalue solver, using MPKs in order to gain a speedup is not a drop in replacement for the SpMV kernel. Changes to the algorithms are required. Assuming that the changed algorithms converge equally well, the use of MPKs is however a possible solution for better hardware utilization.

<sup>&</sup>lt;sup>1</sup>We mean communication in the sense of data dependency and thus the requirement to transfer data in a computer's memory hierarchy. Referenced literature sometimes also uses the term for communication in parallel systems.

#### 1 Introduction

One of the main problems that we see is that most of the research focuses on solutions for CPUs. There is some research being done for GPUs [24], but it is rather outdated as it focuses on the case where matrices do not fit in the Graphics Processing Unit (GPU)'s DRAM [24, p. 1750]. These days single GPUs have enough memory to hold the largest possible Compressed Row Storage (CRS) matrices with 32 bit indices and using multiple GPUs is not as essential as in [37]. Because GPUs have become a very fundamental hardware component for scientific computing we benchmark and analyze what level of performance can be expected with the use of MPKs. A core concept our work is based upon is a cache blocking strategy which was originally designed for Central Processing Units (CPUs) [1].

In this thesis we will show the context in regards to related work, discuss the technical fundamentals, and explain how the cache blocking strategy works that we build upon. Using this knowledge we show how we created a cache blocked MPK benchmark for GPUs. We then discuss its optimization and evaluate its performance to show what the challenges and benefits are.

# 2

# FUNDAMENTALS

## 2.1 Related Work

The disproportionate increase of memory bandwidth compared to computation speed is no new phenomenon [4, 23, 36]. Accordingly, utilizing the available bandwidth has become more and more crucial. To alleviate this problem, caches have been introduced a long time ago and they usually work well for general purpose applications. However, for larger data sets which do not fit in cache, this usually does not pay off. Therefore *blocked* (or *cache blocked*) algorithms have become an area of research in scientific computing already more than 30 years ago with the goal of avoiding unnecessary or repetitive memory transfers. One of these examples is "The cache performance and optimizations of blocked algorithms" [19]. Its authors take a very fundamental approach at better utilizing cache for dense matrix-matrix multiplications. As for many other cache blocking techniques today, the used core concept is partitioning of the matrix into smaller blocks which fit into cache and consecutively to correctly reorder the processing of these blocks to improve cache reuse.

Their focus is primarily on modelling cache hit and miss ratio depending on the blocking sizes and the cache's parameters, not just including the cache size but also line size and associativity. Unfortunately, the paper's applicability for our research is limited. There is, of course, no roofline based analysis in regard to compute and memory performance, as it has been introduced much later [34]. In addition, compute hardware has vastly changed in favor of multi core computers with highly optimized cache hierarchies. One of the conclusions the authors make is that for a block size "the optimal choice occupies only a small fraction of the cache, typically less than 10%" [19, p. 73]. We assume that this is likely different with today's vastly more efficient hardware.

Albeit older, a more relevant paper is "Implicit and Explicit Optimizations for Stencil Computations" [14]. It discusses the influence of caches on stencil based algorithms like partial differential equation solvers. While they explicitly only discuss stencils, this can still be considered relevant, as stencil operations can be mapped to sparse matrices, which are discussed in this thesis. They present multiple algorithms, starting from a naive implementation, going over to an "implicitly blocked" [14, p. 53] variant to an explicitly blocked algorithm [14, p. 55]. The key concepts they use to improve cache reuse are spatial reuse, which is data reuse within a single stencil sweep and temporal reuse, which is reuse of data across multiple stencil sweeps.

Considering the context of this thesis, there are two reasons why we believe the spatial reuse is less relevant. First, today's compute hardware has changed a lot with better caches and execution pipelines which we expect to be better at hiding instruction latency. We mention this because the authors explicitly discuss SIMD and other techniques as means to hide latency from the compute architecture and we assume this to be negligible for our context. Second, processing sparse matrices is generally even more data intensive than processing stencils, since the matrix data has to be loaded

#### 2.1 Related Work

also. In addition, this matrix data cannot be reused spatially. In contrast, we think that their concept of temporal reuse is a lot more applicable to our goal, especially since a few other papers use similar techniques to speed up subsequent SpMV operations. These papers are reviewed below.

Stencil based solvers are only a subset of sparse matrix based solvers, as stencils are usually implicitly defined by the algorithm instead of a matrix which has to be stored separately. Operating on matrices instead makes it more difficult to generalize what the authors call "time skewing" [14, Fig. 5]. By that they mean a special execution order in which data is accessed that is optimized on cache reuse. Following this execution order is difficult for matrices because they do not necessarily have well structured data dependencies compared to stencils. In contrast, a very recent attempt at a general approach for matrices is done with Recursive Algebraic Coloring Engine (RACE) that we utilize for our work.

However, before discussing RACE, we cover earlier approaches such as done by Demmel et al. [6] which try to apply a blocking strategy for sparse matrix solvers. The authors introduce the concept of Matrix Power Kernels (MPKs) as means to reduce *communication* in KSMs in order to get a modelled speedup in the range of  $1.3 \times$  to  $22.2 \times$  [6, Fig. 3, Tab. 3]. At this point an important distinction has to be made as in our thesis we solely discuss local speedup on a single chip. In the cited paper the highest of the performance figures are modelled after a cluster system connected over the internet with much higher latency and bandwidth restrictions. While it does fall under the category of *communication avoiding*, as it reduces memory traffic, that model is not applicable for our case. More comparable speedups are the ones modelled with what they call "CacheBlocked" [6, Tab. 3]. Although algorithmically the same as *CacheBlocked*, their "OOC" model is not a good comparison for today's hardware, since it is based on mechanical hard drives. Nowadays these are usually replaced by faster solid state drives and are often irrelevant during the actual computation, as DRAM capacity has become large enough.

Interestingly, their sequential algorithms works similarly to the *time skewing* technique from "Implicit and explicit optimizations for stencil computations", which is referenced previously. In addition there is a further restriction which Demmel et al. have made in regards their sequential algorithms because they only work for sparse matrices that "partition well" [6, p. 1]. This means that the sparse matrices cannot have an arbitrary structure and need to have a grid structure in the graph that represents them. Therefore the applicable problem class is de-facto the same as stencils with the exception that a matrix can have arbitrary weights for each value while a stencil is typically fixed for the entire grid it is applied upon. So this approach is stil not a solution for general sparse matrices.

In a later publication Demmel et al. discuss an MPK alteration of the widely known Generalized Minimal Residual Method (GMRES) [29] algorithm which they call "Communication-Avoiding GMRES (CA-GMRES)" [25, Sec. 4]. Considering the most expensive operations only, they replace the SpMV and the Modified Gram-Schmidt (MGS) from the main loop with an MPK and a TSQR decomposition. They do this similarly to previous ideas [3, 13] of performing GMRES differently, except previous solutions do not use MPKs. Performance measurements are also available and in opposite to the authors' previous papers this one explicitly excludes a "multinode implementation" [25, p. 2]. The speedup for CA-GMRES on their Intel Clovertown system ranges from  $1.6 \times$  to  $4.3 \times$  for different types of matrices.

We should note that these improvement figures refer to the entire CA-GMRES, not just the MPK. Our analysis in Chapter 4 will only discuss MPKs and not the performance of linear solvers, so care should be taken when comparing these results. In addition, since the paper was published in 2009, hardware has yet again increased in terms of compute performance, memory, and cache capacity. Thus have the matrices of interests, as the distinction between cached and uncached performance is of no relevance if the matrices fit in the cache. Nevertheless, when applying this for larger matrices, their conclusion about speedups in regards to rising relative communication costs compared to floating point performance is still reasonable, as this trend has not changed.

A more comprehensive collection of communication avoiding KSMs is published in [12]. They discuss not only the fundamentals of KSMs but also multiple algorithms such as the previous *CA-GMRES* and also CA variants of CG [10] and Lanczos [20]. As their process shows [12, Chpt. 5] adapting an algorithm to avoid communication is by no means trivial and it means that SpMVs are not simply replaced by MPKs for better performance. However, it demonstrates that doing so is possible and that MPKs can be used to speed up real world solvers.

Last we mention more recent research in regards to MPKs and possibilities to replace classic SpMV in linear solvers. The authors of [1] demonstrate the use of the Recursive Algebraic Coloring Engine (RACE) to get speedup for MPKs ranging from  $3 \times to 5 \times$  on modern multicore CPUs. As recent chips have seen high increases in L3 cache sizes, this becomes especially relevant since applying cache blocking becomes more effective the more data can be reused. Because the research and analysis of this thesis makes extensive use of RACE we dedicate a separate section to how it works (see Section 2.8).

## 2.2 Outlook

Before discussing the technical fundamentals that we base our work upon we give an outlook on this thesis. We can assume that MPKs play an important role in making future KSM based linear solvers faster, but so far we have discussed very little about computations on GPUs. These days many computations are done on GPUs to take advantage of their higher peak performance and bandwidth. For example, a recent state of the art AMD EPYC 9654P is rated at a maximum nominal memory bandwidth of 460 GB/s [2] while an Nvidia H200 GPU is rated for up to 4800 GB/s [27]. The related research we could find in regards running MPKs on GPUs limits itself to avoiding communication in parallel multi-GPU configurations [37]. However, little to no attention is being focused on sequential execution on single GPUs. Because there is so little research in that regard, we explore the possibilities of performance improvements from MPKs over traditional SpMV on GPUs.

While our detailed analysis will present performance models, one main goal is to perform real measurements on GPUs. We start with a brief summary of GPUs and systems we used. We proceed by creating a standard roofline model based on nominal performance figures for the classic SpMV. Later we will perform measurements with our custom benchmark called *MPK-HIP* and as its name suggests it is written using Heterogeneous Interface for Portability (HIP). This benchmark makes use of common sparse matrix formats for which we also will provide a short overview. As we consider the HIP language to be not so common, we will also provide a brief overview of the language and why we chose it. We continue with a compact introduction into GPU programming and general guidelines for achieving good performance. Last we summarize the functionality of the fundamental building block RACE. This will be relevant for interpreting its performance results later.

## 2.3 Hardware Selection

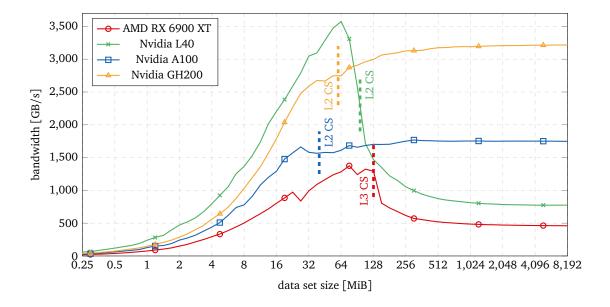

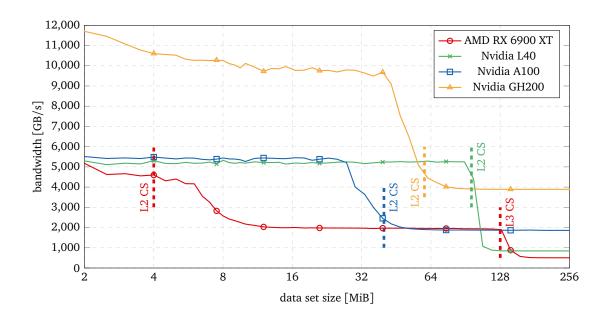

Recent GPUs have experienced a disproportionate jump in Last Level Cache (LLC) capacity (see Table 2.1). Considering the general increase in computing power for computer hardware, an increase may not be surprising. It is well known that compute performance has increased disproportionately compared to memory performance and thus bandwidth limited algorithms have not benefitted as

#### 2.3 Hardware Selection

much from that increase. Due to this, caches are traditionally used to relieve the memory interface by providing greatly increased bandwidth for smaller data which fits in the cache. This usually occurs implicitly, but the performance may greatly depend on how the programmer hints the processor to perform its memory accesses. As our goal is to utilize the cache more efficiently one can assume that benefits from larger than usual cache sizes are likely.

Before we discuss any of the caching in regards to MPKs, the first step is to choose suitable hardware for benchmarking. As our main goal is cache blocking, we aim at GPUs with higher than usual caches or GPU which are very common. Table 2.1 shows a summary of datacenter and selected consumer GPUs but most of the GPUs disqualify themselves due to their age and small cache. While the AMD MI300X clearly holds the lead with 256 MB, it was unfortunately not available to us at the time. It is followed by the AMD RX 6900 XT with 128 MB, then by the AMD RX 7900 XTX and Nvidia L40 with a slightly smaller 96 MB cache. We chose to use the AMD RX 6900 XT and Nvidia L40 for our testing. The former one due to its high cache size and the latter due to being from a different vendor. As they are a very widespread GPU, final results in Chapter 4 also include results of the Nvidia A100 and H100. Other GPUs are not covered, as we consider their cache size to be too small.

The Nvidia L40 is sold as a data center supported GPU, but the underlying chip is the same as the consumer Nvidia RTX 4090, so we consider this as a de facto consumer GPU. Their main difference being that the Nvidia L40 has fully enabled cache. As it has slightly less LLC compared to the AMD RX 6900 XT we initially did not consider it, but as we later discovered it proved to be a very favorable GPU for MPKs. A complete list of the hardware used can be seen in Table 2.2. For convenience we refer to these systems by their abbreviation.

| GPU             | Date | Memory  | DRAM type | DRAM bandwidth | LLC size |

|-----------------|------|---------|-----------|----------------|----------|

| Nvidia K40      | 2013 | 12 GiB  | GDDR5     | 288 GB/s       | 1.5 MiB  |

| Nvidia M40      | 2015 | 24 GiB  | GDDR5     | 288 GB/s       | 3 MiB    |

| Nvidia P100     | 2016 | 16 GiB  | HBM2      | 732 GB/s       | 4 MiB    |

| Nvidia V100     | 2017 | 32 GiB  | HBM2      | 900 GB/s       | 6 MiB    |

| Nvidia A100     | 2020 | 80 GiB  | HBM2e     | 2039 GB/s      | 40 MiB   |

| Nvidia H100     | 2022 | 80 GiB  | HBM3      | 3352 GB/s      | 50 MiB   |

| Nvidia H200     | 2023 | 141 GiB | НВМЗе     | 4800 GB/s      | 60 MiB   |

| AMD MI100       | 2020 | 32 GiB  | HBM2      | 1229 GB/s      | 8 MiB    |

| AMD MI210       | 2021 | 64 GiB  | HBM2e     | 1638 GB/s      | 8 MiB    |

| AMD MI250       | 2021 | 128 GiB | HBM2e     | 3277 GB/s      | 16 MiB   |

| AMD MI300X      | 2023 | 192 GiB | HBM3      | 5171 GB/s      | 256 MiB  |

| AMD RX 6900 XT  | 2020 | 16 GiB  | GDDR6     | 512 GB/s       | 128 MiB  |

| Nvidia A40      | 2020 | 48 GiB  | GDDR6     | 695 GB/s       | 6 MiB    |

| AMD RX 7900 XTX | 2022 | 24 GiB  | GDDR6     | 960 GB/s       | 96 MiB   |

| Nvidia L40      | 2022 | 48 GiB  | GDDR6     | 864 GB/s       | 96 MiB   |

**Table 2.1** – Memory and last level cache of recent GPUs. The first group shows Nvidia data center GPUs, the second group shows AMD data center GPUs, and the third group shows GPUs with consumer chips.

| Abbrev. | CPU                      | RAM      | GPU                          | OS              |

|---------|--------------------------|----------|------------------------------|-----------------|

| RX 6900 | 2x Intel Xeon E5-2620 v4 | 64 GiB   | AMD RX 6900 XT               | Ubuntu 22.04.04 |

| L40     | 2x AMD EPYC 9354         | 768 GiB  | Nvidia L40                   | Ubuntu 22.04.04 |

| A100    | 2x AMD EPYC 7713         | 2048 GiB | Nvidia A100 (80 GiB, SXM)    | AlmaLinux 8.9   |

| GH200   | Nvidia GH200             | 480 GiB  | Nvidia H100 (96 GiB, GH200)) | Ubuntu 22.04.04 |

Table 2.2 – Test system specifications.

# 2.4 Approximate Roofline Model

Two of the very fundamental performance metrics of a CPU or GPU are their memory bandwidth and floating point performance. An overview of ideal figures for the tested hardware can be seen in Table 2.3.

Using the standard roofline model we can estimate whether MPKs are memory or compute bound. As approximation we use the best-case performance of the SpMV kernel [35, Eq. 4], which for 64 bit floating point values and 32 bit indices results a *data intensity* of 6 Byte/FLOP. For calculating performance, we use the same symbols as [28][p. 77], meaning *I* for operational intensity, *W* for FLOPs, *T* for time, and *Q* for memory traffic. Additionally, we will also define the inverse of operational intensity as  $D = I^{-1}$  for *data intensity* and the bandwidth as  $B = QT^{-1}$  for convenience. Thus:

$$P = \frac{W}{T} = \frac{B}{D}$$

(2.1)

$$P_{\text{RX6900}} = 512 \,\frac{\text{GByte}}{\text{s}} \div 6 \,\frac{\text{Byte}}{\text{FLOP}} \approx 85.3 \,\frac{\text{GFLOP}}{\text{s}}$$

(2.2)

$$P_{L40} = 864 \frac{\text{GByte}}{\text{s}} \div 6 \frac{\text{Byte}}{\text{FLOP}} \approx 144.0 \frac{\text{GFLOP}}{\text{s}}$$

(2.3)

$$P_{A100} = 1940 \frac{\text{GByte}}{\text{s}} \div 6 \frac{\text{Byte}}{\text{FLOP}} \approx 323.3 \frac{\text{GFLOP}}{\text{s}}$$

(2.4)

$$P_{\rm GH200} = 4000 \, \frac{\rm GByte}{\rm s} \div 6 \, \frac{\rm Byte}{\rm FLOP} \approx 666.6 \, \frac{\rm GFLOP}{\rm s} \tag{2.5}$$

These are approximate figures, yet all the performance numbers are significantly lower than the nominal floating point performance of each GPU. This is the case even when considering that the RX 6900 and L40 have low double precision performance, which is relatively common for consumer chips. According to this basic roofline model, there is a very clear memory bandwidth limit. We discuss more precise figures in Section 4.4.3 as they then depend on the matrix due to row overhead.

| GPU                   | GFLOP/s (SP) | GFLOPS/s (DP) | GB/s (DRAM) |

|-----------------------|--------------|---------------|-------------|

| AMD RX 6900 XT        | 23,040       | 1,440         | 512         |

| Nvidia L40            | 90,520       | 1,414         | 864         |

| Nvidia A100 (80 GiB)  | 19,490       | 9,746         | 1,940       |

| Nvidia GH200 (96 GiB) | ~67,000      | ~34,000       | ~4,000      |

Table 2.3 - Nominal GPU performance and bandwidth figures.

## 2.5 Sparse Matrix Formats

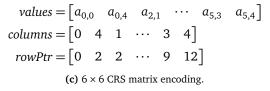

#### 2.5.1 CRS

For many problems in linear algebra, matrices are only populated sparsely which means that a large percentage of coefficients are zero. For example, a matrix may have millions of rows, but only in the order of ten values per row. If only the non-zero values of this matrix were stored in memory, only approximately 10 million values must be stored. This is easily accomplished with today's computers. In contrast, if the matrix was stored entirely in a dense fashion, trillions of values would have to be stored and processed, which is too much for even a computer with large memories. To overcome this, the Compressed Row Storage (CRS) format is commonly used to store matrices more compactly (see Figure 2.1), which in turn results in more efficient calculations.

The coefficients are stored row-wise in the *values* vector without zeroes. A second vector with the same length called *columns* stores the column index of the original matrix. It is then possible to reconstruct the original matrix by adding a third vector *rowPtr* which stores the index the rows start at in the former two vectors. The length<sup>2</sup> of each row is implicitly determined by the start of the next row.

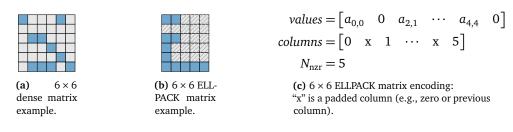

#### 2.5.2 ELLPACK

The ELLPACK format can be considered a simplification of CRS as it simply omits the *rowPtr* vector. To be able to reconstruct the original matrix, each row must be equally long since *rowPtr* and *columns* then become a linearized 2D-array. One of the indices is the row's coordinate and the other one is the row index (see Figure 2.2).

Since the resulting data (see Figure 2.2b) is 2D it can be stored row-wise or column-wise, but it typically is stored column wise. Although ELLPACK omits the *rowPtr* vector, it is usually less memory efficient than CRS since all rows have to be padded to the longest row's length. One of its benefits is the option for a column major layout, which improves performance for GPUs, because memory accesses are continuous among threads instead scattered. We discuss these performance implication in more detail in Section 3.2.6.

#### 2.5.3 SELL-C- $\sigma$

In the general case ELLPACK is not a viable option, as it deals very poorly with uneven row lengths. There have been multiple propositions [32, 7, 18] to circumvent ELLPACK's memory and computation overhead. One category of these alterantives are the Sliced ELLPACK (SELL) formats [26, p. 115]. What SELL attempts is to reduce the padding overhead of ELLPACK by slicing the matrix into blocks

<sup>2</sup>By *row length* we refer to the number of non-zeroes per row ( $N_{nzr}$ ).

Figure 2.1 – CRS format.

Figure 2.2 – ELLPACK format.

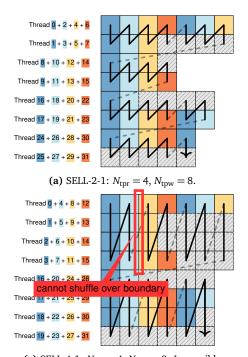

of rows, which are padded only to the block's maximum row length. A universal and well performing variant is the SELL-*C*- $\sigma$  format [17, p. 9]. It uses fixed size blocks or *chunks* of size *C* which is chosen to best fit the compute architecture. When *C* is chosen for example according to the Single Instruction Multiple Data (SIMD) width, the chunk can be read and processed without shuffling. Additionally it specifies a sorting scope  $\sigma$  to order the matrix in blocks of length  $\sigma$ . This is intended to reduce padding in the *C* sized chunks (see Figure 2.3c). This implies  $\sigma > C$  to get any benefits because sorting just inside of a chunk will not reduce the chunk's maximum row length. If no sorting is desired or possible,  $\sigma = 1$  is assumed. As we will discuss later in Section 3.2.6, no sorting is done in our examples.

Figure 2.3 shows an example for C = 2,  $\sigma = 1$  and  $\sigma = 8^3$ . For SELL-*C*- $\sigma$  the start of a row can be calculated by first determining the chunk and retrieving its start index via *chunkPtr*. The relative position inside the row can be determined by its internal position just like with regular ELLPACK by using the row's length of its chunk from *chunkLen*.

To conclude, SELL-C- $\sigma$  is useful because, unless for extreme cases, it allows to get a good compromise between compactness of CRS and GPU performance from ELLPACK. Accordingly, it is one of the preferred matrix formats we discuss later for benchmarking in Section 3.2.6.

<sup>3</sup>We use the *C* and  $\sigma$  in SELL-*C*- $\sigma$  to specify its parameters: E.g., SELL-*C*- $\sigma$  for *C* = 2 and  $\sigma$  = 8 would be SELL-2-8.

$\sigma = 8$ sorted С CС С (a)  $8 \times 8$  dense matrix (b) 8 × 8 SELL-2-1 ma-(c) 8 × 8 SELL-2-8 maexample. trix example. trix example.  $values = \begin{bmatrix} a_{1,0} & a_{1,1} & a_{1,3} & \cdots & a_{3,7} & 0 \end{bmatrix}$  $values = \begin{bmatrix} a_{0,0} & a_{0,4} & 0 & \cdots & a_{7,6} & 0 \end{bmatrix}$  $columns = \begin{bmatrix} 0 & 4 & x & \cdots & 6 & x \end{bmatrix}$  $columns = \begin{bmatrix} 0 & 1 & 3 & \cdots & 7 & x \end{bmatrix}$ *chunkPtr* =  $\begin{bmatrix} 0 & 10 & 14 & 20 & 28 \end{bmatrix}$ *chunkPtr* =  $\begin{bmatrix} 0 & 10 & 16 & 20 & 24 \end{bmatrix}$  $chunkLen = \begin{bmatrix} 5 & 2 & 3 & 4 \end{bmatrix}$  $chunkLen = \begin{bmatrix} 5 & 3 & 2 & 2 \end{bmatrix}$ (d) 8 × 8 SELL-2-1 matrix encoding: (e) 8 × 8 SELL-2-8 matrix encoding: "x" is a padded column (e.g., zero or previous "x" is a padded column (e.g., zero or previous column). column).

**Figure 2.3** – SELL-*C*- $\sigma$  format.

#### 2.5.4 Matrix Format Restrictions

Generally, the matrix formats above can use any available primitive data types supported by the compute architecture. Due to implementation restrictions of RACE (see. Section 2.8), we will only consider a single set of data types in this thesis. For floating point values we only use 64 bit double precision and 32 bit integer values for index values. Changing these types may affect performance, as different hardware processes double and single precision floats at different speeds, and the required memory of values affects the needed memory bandwidth.

## 2.6 HIP Language

As of today GPUs are most commonly programmed using the Compute Unified Device Architecture (CUDA). This has the inherent limitation of being limited to Nvidia GPUs, and as we have discussed previously in Section 2.3 we intend to target AMD GPUs as well. HIP [11] is a language which solves this as it is compatible with both AMD and Nvidia GPUs. Unlike OpenCL, porting code from CUDA to HIP is very simple and its API is, with the exception of the *hip* instead of *cuda* prefix, mostly identical. Due to this difference in prefixes, changes to the source code are necessary. For simple programs this can be automated by *hipify.pl* which comes with the ROCm toolchain. The code can then be compiled via *hipcc*, which serves as frontend for *nvcc* (Nvidia) or *clang* (AMD).

In a few cases small adjustments to the code are still necessary. For example, the commonly used *\_\_shfl\_XYZ\_sync* functions are not available with HIP and have to replaced by their *\_\_shfl\_XYZ* equivalent. This is partially caused by architectural differences, because certain AMD GPU differ in warp size and thus cannot use the same function signature.

Once the code works for both vendors, the performance can be expected to be equal to a native CUDA program on Nvidia because HIP's API is simply a header-only wrapper. No additional cost is added, since most function calls from *hipXYZ* forward inline to *cudaXYZ*. As HIP is developed by AMD, we do not expect significant performance penalties from using HIP over OpenCL on AMD. We did not opt for the latest available ROCm version 6.0.0 for Nvidia GPUs, as we were unable to build the HIP API with Nvidia support. More details with regard to software versions are shown in Section 3.2.2.

### 2.7 GPU Programming Introduction

As GPUs have become very widespread and processors have become more parallel instead of higher clocked, the implementation of parallel programs becomes more and more relevant to allow efficient scalability [8]. When a program for CPU is written, hardly any restrictions exist in terms of concurrency. Today's top of the line multi-core processors have 128 cores, but the threads which run on them are usually fairly independent. Consequently each core has its own execution pipeline, a private L1 cache, possibly shared with a single or a very low amount of threads which share the same resources. In contrast GPUs are optimized for processing high amounts of data in a more parallel and regular manner as each "core" usually consists of many threads which run in lockstep. Although CPUs have also gained the ability to process data concurrently on each core via SIMD, on GPUs this is usually implemented via Single Instruction Multiple Threads (SIMT).

Accordingly a number of implications exist. A CPU software library like RACE is written in C++ and cannot run on GPUs. There are of course language extensions like CUDA, which as of today is likely the most widespread language for GPU applications. However, it cannot port software to run on GPU without explicit changes. One of the most fundamental requirements for GPU code are

Adapting existing code for CUDA is the first step, but a correct program does not guarantee good performance. The solely reason for porting software to GPU is to get superior performance compared to CPU. Of course general rules for optimization exist for GPUs as they do for CPUs, like reducing algorithmic complexity, reducing code size, avoiding data dependencies, or to avoid branching. But due to their architecture, GPU programs have the following constraints that do not necessarily apply the same way for CPU:

- **Kernel Launch Overhead:** The GPU code is only run via explicit calls from CPU, and for each issued call, CPU to GPU communication is required. In practice, the CUDA runtime can avoid this to a certain extent by batching multiple kernel calls, but even with batching, each new kernel call requires new threads to be launched. It is possible to explicitly batch kernel calls in the CUDA language via *graphs*. That way the driver knows the code and the number of threads ahead of time and can schedule execution more ideally. We will later demonstrate that both number of threads per call (see Section 4.4.2.4) and batching (see Section 3.2.8) can impact the performance.

- Synchronization Barriers: While a high number of kernel launches may be limited by the amount of threads the GPU can launch, such a kernel launch always acts as synchronization barrier on the GPU. This provides the programmer a way to avoid race conditions on GPU, but it can cause ramping effects as hardware has to wait for all affected GPU threads to finish before starting new ones. Solving this is similarly affected by solving the kernel launch overhead, as it usually requires minimizing the number of kernel calls. Alternatively, if applicable, fewer synchronizing events have to be used if multiple kernels run concurrently.

- Uncoalesced Memory Access: We previously discussed the way hardware threads are organized on GPUs. The smallest group of hardware threads, commonly called *warps*, have a size of 32 on Nvidia GPUs. As these threads typically run in lockstep, all threads will run the same instruction simultaneously. Newer Nvidia GPUs introduced *independent thread scheduling*. Since this doesn't change the general trend how to write good GPU code, it is not covered here. For example, if a multiply instruction is executed, all threads execute this instruction simultaneously. This works well for arithmetic, as it will only interact with data from the local register file. However in case a memory fetch is issued by all 32 threads, the addresses may be arbitrarily scattered in memory. It is well known that random access causes worse performance compared to sequential access, and this applies for GPUs as it does for CPUs. Since the number of running threads on GPUs is much higher than on CPUs this effect becomes significantly more relevant. Threads "prefer" to access memory in a single block, because the memory controller can then for example fetch 32 subsequent *double* values from memory in a single run. If the memory is not accessed sequentially, this may severely impact the performance,

especially on AMD GPUs (see Section 3.2.5). It is also noted that this means data is interleaved for all 32 threads as shown in Figure 2.4 and not ordered sequentially for each thread.

- **Code Branching:** As for the previous point, similar restrictions apply for conditional branches. When optimizing code for CPUs, code branching can be reduced to avoid mispredicted, and thus penalized, branches. On GPUs this is usually problematic due to the lack of branch prediction. Instead, the reduction of diverging branches is more relevant. Once a thread branches to a different target than the ones in the same warp, it can possibly stall all other threads within that warp.

- **CPU-GPU data exchange:** Because the compute work for GPU is dispatched from CPU, the data set, in our case a matrix and a vector, has to be transferred from CPU to GPU before running the kernel. Accordingly the results have to be transferred back to the CPU. This imposes a possible transfer bandwidth limitation and a synchronization barrier. This is however only relevant for the start and end of computation. If all computation is done on GPU, no data exchange is necessary between kernel calls. For problems involving many iterations this can usually be ignored.

Except the last of point, all will be relevant for the following chapters. We will reference them accordingly for certain design decisions we made.

## 2.8 RACE and Level-Based Cache Blocking

The proposed solution to GPU accelerated MPKs is primarily based on the Recursive Algebraic Coloring Engine (RACE) [1]. RACE is a software library which implements a temporal blocking algorithm. This is used to better utilize the cache during MPK calculation. This section briefly explains how RACE works and how it creates the fundamental building block for the later used benchmark implementation called *MPK-HIP*.

One of RACE's first steps is to apply a transformation to the matrix to make it more diagonal and thus more "cache-friendly" [1, p. 586]. This transformation, which is solely a row and column

**Figure 2.4** – Memory Coalescing: The black arrow denotes the ideal data ordering for memory read/write coalescing ( $N_{tpw} = 8$ ). As all threads in a warp execute the same instruction at the same time, they should operate on a continuous block of data for every memory operation.

permutation, is non-optional and is also required for the implementation of *MPK-HIP*. Matrix permutations are commonly used to speed up SpMV [15], and we will assume that its gains will generally outweigh its costs. As RACE uses an algebraic graph-based approach, the input matrix does not require any specific shape [1, p. 581], but of course the gains are limited to the possibilities of permutations and cannot fix a random sparse matrix.

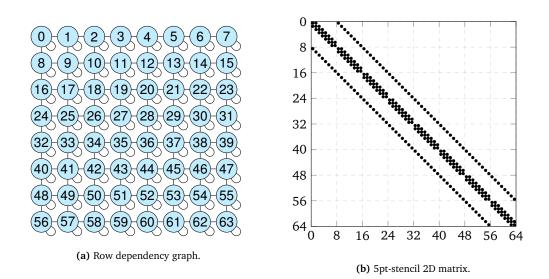

For better illustrating RACE's exact functionality, we use a simplified 2D-5pt stencil matrix instead of a 2D-7pt stencil as originally published in [1, p. 586] in an  $8 \times 8$  grid. This stencil's matrix is shown in Figure 2.5b along with its graph<sup>4</sup> in Figure 2.5a. With the exception of the edge cases, the matrix has a diagonal shape. Because calculating matrix powers involve successive SpMV operations, these SpMV operations can be characterized by row dependencies. This is meant in the sense, that each output vector component for an SpMV operation depends on a set of input vector components, which can then be represented as a graph. In this graph, each vertex represents a row, and an edge forms a dependency of a row with another row. The corresponding example graph is shown in Figure 2.5a. Since a 2D-5pt stencil is used, each row's dependencies are its vertical and horizontal neighbours but also the row itself.

This graph becomes relevant when attempting cache blocking, because it restricts which data may be retained in cache, and which data is required to be fetched from memory. In order to calculate one power iteration for a certain row, the graph has to be traversed from that row's vertex by a depth of one in order to determine which input rows are required. For cache blocking it is necessary that these inputs rows stay in cache as much as possible, but for an arbitrary matrix power this is impossible. In that case the graph will be traversed completely at some power. Thus all the rows must be kept in cache, which is not possible. RACE attempts to solve this limitation by a calculation order strategy which ensures that data fetched from memory will stay in the cache as long as it still needed for calculation. A matrix that already fits in the cache would of course not benefit either way.

<sup>4</sup>We use the term *graph* or *dependency graph* as means for the equivalent matrix interpreted as adjacency matrix.

**Figure 2.5** – 2D 5pt-stencil matrix structure and dependency graph. A vertex represents a row of the matrix. An edge denotes a dependency and points to another row which is needed for the other row's calculation [1, Fig. 4].

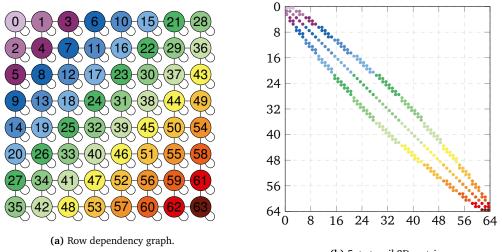

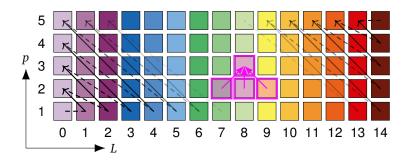

While the previously mentioned permutation step does improve cache-friendlyness it is also fundamental to RACE's "level formation" [1, p. 586]. These levels are key to define the calculation order of the final matrix power. In this formation step rows are assigned to a level number in such a way that all rows in a level only depend on other rows of neighbouring levels. The way the level numbers are assigned is a traditional Breadth-First Search (BFS) where the depth of the search defines the level number, and the search order of the rows defines their new row. Thus each depth descent in a BFS searches the required dependencies for one additional power iteration.

The level formation and the reordering is shown in Figure 2.6a. All vertices now have a different number assigned which refers to the new row they have been reordered to. As expected, the numbers occur in the BFS order from the starting row zero. Each BFS descent is shown as new level in a separate color and as reordered matrix in Figure 2.6b. The graph layout is unchanged, as dependencies are neither introduced nor removed.

We assume that once an SpMV is executed on a single level, its output will stay in cache. If p = 1 is calculated all inputs will not be in cache. One can then use an execution order illustrated in Figure 2.7 (black arrows) to maximize cache reuse. Because all rows in a level only depend on rows of their neighboring levels, a level's power p + 1 can be calculated fully cached as soon as its neighbouring levels' power p are calculated (pink arrows). Each square represents an SpMV operation to calculate a level's power. If the execution is performed in the demonstrated order, at most p + 1 levels will have to stay in cache. In theory only p levels have to stay in cache due to the diagonal traversal, but because caches often employ a LRU eviction policy, it is p + 1 in practice. With this order a level is fetched from DRAM only for its first power calculation. This is similar to the sequential algorithms for communication avoiding KSMs that we discussed previously in Section 2.1.

Because level size can be very small and possibly very unequal in size, RACE forms *level groups* as an additional optimization step. The approach is to reduce execution overhead by being able to perform larger continuous SpMV operations by merging multiple levels into one. There is generally no downside to forming as large level groups as possible, but eventually an increase will hit a cache size boundary where p + 1 level groups no longer fit in the cache. This boundary is also mentioned

(b) 5pt-stencil 2D matrix.

**Figure 2.6** – 2D 5pt-stencil matrix structure and dependency graph after BFS reordering matrix from Figure 2.5. Each color represents an assigned level and each level's rows only reference rows from themselves or neighbouring levels [1, Fig. 4].

**Figure 2.7** – *Lp* diagram: Black arrows denotes the most cache efficient execution order. Each square represents an SpMV performed on the respective level [1, Fig. 5]. When following this order, at most p + 1 = 6 levels have to be retained in cache in order to avoid DRAM loads for  $p \neq 1$ . If for example  $L_{p=5}(0)$  is calculated that level is no longer needed, but  $L_{p=1}(5)$  will not evict L(0) from cache due to being used just before. This is why p + 1 levels need to fit in cache instead of p. The pink arrows show which data level L = 8, p = 3 needs for its calculation. The diagram applies for levels and level groups equally.

in [1, Eq. 5] and accounts for the non-zeroes in the matrix data. [1] does not mention result vectors explicitly, but it is rather simplified in a safety factor which accounts for all other data overhead as well. We will discuss this safety factor later in Section 4.4.2.5 as it can have an effect on the cache blocking efficiency.

In contrast to being small, a level can also be too large. That is the case if p + 1 levels of that size can no longer fit in cache. RACE supports a way to split larger levels into smaller ones using "Recursion" [1, p. 590]. However due performance penalties of more fine grained execution flow (see Section 4.4.2.4), we have not analyzed it in our work.

When the programmer utilizes RACE the level and group forming is abstracted away. Consequently only the reordering has to be performed as supplied by RACE, and and SpMV kernel must be provided. Because RACE has to be able to perform SpMV on individually formed level groups, not all SpMV kernels can be used since they usually do not support execution on a subset of rows. This unfortunately includes commonly used math libraries such as *cuSPARSE*. That is why we chose for a custom kernel implementation, which we cover in more detail in the following chapter.

# **IMPLEMENTATION**

# 3

## 3.1 Benchmarking Goals

The main objective we are aiming for is to reliably evaluate performance of MPKs on different hardware configurations. We already mentioned briefly in Chapter 1, the core of this thesis is the *MPK-HIP* benchmark. Before discussing its functionality in the following subsections it is important to elaborate the actual goals of this benchmark and its results.

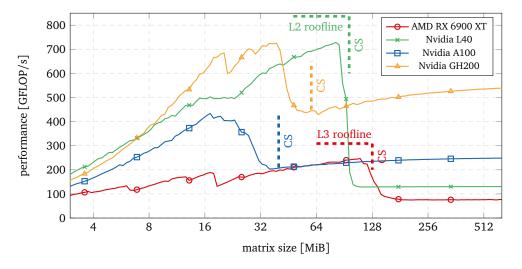

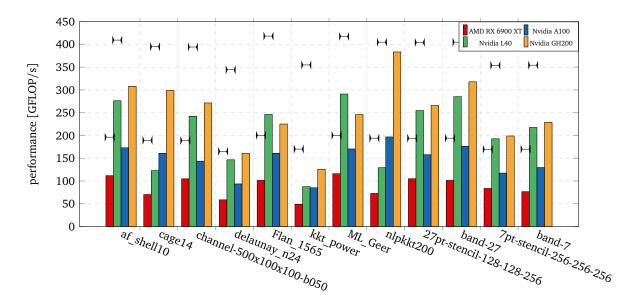

Fundamentally, a benchmark is supposed to allow "evaluation of the speed of the compilation and execution" [22, p. 83] of software. The general intention is to analyze our improvements to linear systems solvers. It is commonly known that SpMV operations, or in our case MPKs, are the most limiting factor. Thus we can limit our benchmark to this particular matrix power *kernel*. In addition to just running our own custom kernel, it is pivotal to judge whether it runs at the speed it is expected to. For example, the results should follow the *roofline* model [33], alternatively it should be understood why the benchmark does not perform as expected compared to the roofline. Unless optimized MPKs vastly change the compute-to-bandwidth ratio compared to regular SpMV, they are expected to be severely bandwidth limited. In our case this is likely not the case, as RACE does not alter the total amount of computation nor reduces the amount of data compared to regular SpMV based MPKs. However, we can still expect a speedup with RACE, as caching will raise the bandwidth limit effectively. Running into a compute limit will not be a problem. If we recall Table 2.3, this would require speedups over 10×, which would be very optimistic.

## **3.2 MPK-HIP**

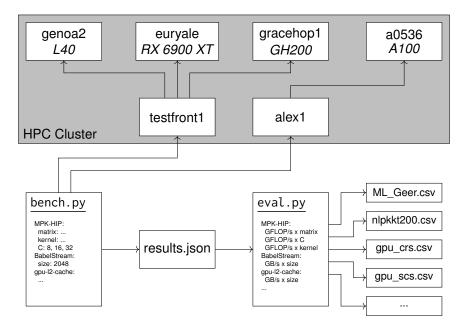

#### 3.2.1 Benchmark Build Setup

In this section we present our benchmark *MPK-HIP*, explain how it works, and what it measures. We briefly mentioned the CUDA language as means to program GPUs. As one of our test systems features an AMD GPU, CUDA cannot be used. For older GPU generations OpenCL used to be the common choice for AMD. However since OpenCL is known to run worse on Nvidia GPUs [16], and to ease porting, AMD ROCm introduced HIP. This created an easier way to run the same code for both Nvidia and AMD GPUs. We chose HIP as language in order to run the same benchmark on both vendors' GPU to avoid relying on multiple benchmark codebases, which could possibly diverge.

Many benchmarks traditionally have a very simple build setup. Commonly just a single Makefile and a single source file. GNU Makefiles can of course be used with multiple source files, but the HIP language leads to a non trivial setup, as manually setting up vendor specific compiler paths and include directories becomes rather cumbersome. In addition, MPK-HIP also depends on the RACE software library, which uses CMake to manage its builds. As a single source file benchmark is already out of question, and as MPK-HIP also relies on other libraries, using CMake is inherent. While CMake does make managing builds easier, it has the limitation that it makes it harder to run the benchmark on numerous platforms. This is not a limitation in our case, as running code on GPU already vastly reduces the number of hardware architectures. As of today this leads to a modern x86 oder ARM based system with either an Nvidia or AMD GPU. It is unlikely that CMake is not available for these, especially considering CMake is recommended by AMD to be used for the HIP language. One of their reasons to recommend CMake is because it natively supports the HIP language and it can compile for both Nvidia and AMD via switch. It does however require the very recent version 3.28 of CMake.

Another practice many benchmarks follow is to ship certain libraries they depend upon. Common examples are argument parsers or matrix file parsers. We excluded this approach, as CMake already provides a way to fetch and find required libraries via *FetchContent* and *find\_package*. Consequently it keeps the actual benchmark free of unrelated code. This approach may lead to the benchmark being more prone to build failures, as it depends on libraries which may not be as easily obtainable in the future. However, since the ROCm libraries are non-trivial to setup and cannot be included in the project in the first place, this becomes comparatively less of a problem.

In the end, compiling MPK-HIP is as simple as compiling any other CMake based project. The user runs cmake ... in the build subdirectory and optionally specifies -DMPKHIP\_GPU\_ARCH to select which GPU architecture to compile for. Alternatively, the included build.sh simplifies the GPU architecture choise by providing an interactive selection.

#### 3.2.2 Dependencies

We will briefly discuss the software libraries MPK-HIP depends on. Some of them provide merely "boilerplate" code for features which C++ natively does not support, like JSON (via *nlohmann::json*), argument parsing (via *argparse*), or modern format strings (via *libfmt*). Others provide more important functionality:

- Eigen: The original RACE CPU benchmark uses custom implementations for dense and sparse matrices. One of the reasons is that the CPU benchmark requires NUMA aware memory allocation to achieve best performance. Since our benchmark runs on a single GPU, Non-Uniform Memory Access (NUMA) nodes are not relevant for kernel execution and no custom allocation is required. Due to this, we chose to use an off-the-shelf solution for matrix handling on CPU before it is uploaded to GPU. In addition we used it to provide a CPU-based reference SpMV implementation for MPK to detect implementation errors.

- **fast\_matrix\_market:** Because MPK-HIP has to ultimately load matrices from disk for benchmarking, a solution for matrix loading is needed. In this chapter we only present results for custom generated stencil matrices, so in theory a custom solution would be sufficient. As other matrices from the SuiteSparse Matrix Collection [31] are discussed in Chapter 4, we chose to use the Matrix Market format. Many existing benchmarks come with the NIST implementation in ANSI C or use a custom parser. We excluded it, as the NIST implementation requires extensive changes to correctly interoperate with modern C++. We also chose against an entirely custom implementation as they often do not support all types of the Matrix Market format. *fast\_matrix\_market* addresses that and in addition it can natively parse matrices into Eigen matrix objects.

• **Thrust:** As MPK-HIP attempts to use modern C++ coding standards, RAII memory management is preferred over manual memory management. For GPU this is achieved by using Thrust's *device\_vector* instead of manual handling via *hipMalloc* and *hipFree*. In addition, it provides type checking for all memory handling outside of the GPU kernels.

A complete list of dependencies and versions is given in Table 3.1.

#### 3.2.3 Operation Procedure

In the following paragraph MPK-HIP's benchmark procedure is shown. The RACE source code comes with example benchmarks, in particular *mtxPower*, which our benchmark is based upon.

- 1. **RACE permutation:** The matrix file is loaded from disk and RACE performs its matrix permutation as explained in Section 2.8.

- 2. **Instantiate Kernel:** Since different types of kernels are implemented, different matrix formats are used on GPU depending on the kernel the user selects. These formats are explained in more detail in Section 3.2.5 and the following sections. It is possible to choose between a fixed-value filled vector or randomly filled vector for matrix power initialization.

- 3. **Warmup:** As the very initial run may exhibit poor performance due to cold caches and unusually high overhead, the kernel is executed a few times. In addition this step checks how many times the kernel has to be called in order to run for a single second. This measurement is performed several times while increasing the call count, since a very low number of kernel calls may still have very high overhead. By increasing the call count that initial overhead is reduced to a minimum.

- 4. **Validation Run (optional):** When implementing a new kernel or determining the accuracy of an existing kernel, it is important to compare the results against a reference implementation. In this step a CPU based implementation is performed via a simple matrix-vector product from the Eigen library. This allows to detect numerical or implementation errors.

- 5. **RACE Kernel Run:** Since the number of iterations has already been determined during warmup, the kernel is now called that number of times. Either it is called directly, or by first recording a HIP graph and then executing this graph (see Section 3.2.8). By running the kernel, we

| Library            | Description                      | Version         |

|--------------------|----------------------------------|-----------------|

| RACE               | MPK cache blocking library       | latest git      |

| ROCm               | HIP language and AMD GPU support | 5.7.1 / 6.0.0   |

| CUDA               | Nvidia GPU support               | 12.2            |

| Thrust             | GPU memory management            | (see CUDA/ROCm) |

| fast_matrix_market | Matrix Market reader/writer      | 1.7.5           |

| Eigen              | Linear Algebra Math Library      | 3.3.8           |

| argparse           | argument parsing                 | 3.0             |

| libfmt             | modern C++ string formatting     | 10.1.1          |

| nlohmann::json     | JSON library                     | 3.11.2          |

**Table 3.1** – List of MPK-HIP's dependencies. ROCm 6.0.0 was only used for AMD GPUs. RACE does not have stable version numbers.

actually refer to instructing RACE to execute the kernel with enabled blocking in order to calculate the requested power. Explicit synchronization barriers (*hipDeviceSynchronize*) are used before the first and after the last iteration to solely measure the time spent on actual kernel execution. Memory copies from or to the GPU are not included.

- 6. **Result Comparison (optional):** If validation was requested previously, the reference implementation is compared to a single kernel run via RACE. The accuracy results are logged accordingly.

- 7. **SpMV Kernel Run:** The purpose of MPK-HIP is to determine whether it is possible to get better performance via RACE. In this last step the same power is calculated with the same number of runs to determine the speedup of RACE compared to an implementation via traditional matrix-vector products. This classic SpMV run uses the already permuted matrix in order to reduce the speedup to effects from cache blocking only.

If no validation is requested, the benchmark will run and output its values as JSON. This allows processing the results via scripting languages. Our exact procedure is explained in Section 3.3.

Unfortunately we discovered a problem with the RACE library where it would ignore the number of threads passed during initialization. When running the benchmark, care must be taken to set the environment variable OMP\_NUM\_THREADS=1. Otherwise RACE may malfunction and cause MPK-HIP to report incorrect results.

#### 3.2.4 Implementation and Optimization

In the following sections we explain the functionality of the most important kernels that we implemented. The same kernel is used to benchmark cache blocked MPK performance with RACE and classic SpMV MPK. Thus optimizations to the kernel will speed up both RACE and SpMV based MPKs.

During optimization we benchmarked these kernels against two standard matrices: A 3D 7pt 256x256x256 stencil matrix and a 3D 27pt 128x128x256 stencil matrix. We chose these as they typically perform better due to their regular structure. The 27pt stencil grid size was decreased to offset for the larger stencil compared to the 7pt. Both matrices do not fit in the cache of any GPU we tested (see Table 4.3).

The code of the kernels that are shown in the following sections are simplified versions only. They do not cover edge cases of HIP block sizes and do not show arbitrary row start and end pointers. Because these cases only slightly change the row index calculation and early kernel returns, we do not consider these relevant in terms of performance.

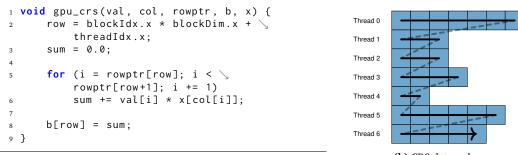

#### 3.2.5 CRS

In this chapter we discuss the first fundamental kernel, which is MPK based on the CRS<sup>5</sup> format. It is very similar to the CRS kernel used in *mtxPower* from RACE's original source code and serves as the first level to compare performance of moving from CPU to GPU. For MPK-HIP and mtxPower, there is no inherent requirement to use the CRS format. This only refers to the calculations since during preprocessing RACE still needs to the matrix in CRS format. For the kernel, the only requirement is that it uses a row based format, which means that rows need support for random access. While the rows are not necessarily processed in a random order, RACE requires its kernel to start and to

<sup>&</sup>lt;sup>5</sup>In practice the terms CRS and CSR are often used interchangeably. As following plots may hint, the MPK-HIP kernel implementations use the term CSR internally.

stop at an arbitrary row when processing a level group. Accordingly, we will also cover other matrix formats than CRS in the following sections.

The basic functionality of the standard CRS kernel and its memory layout is shown in Figure 3.1. In contrast to performing a matrix-vector product on CPU, where one thread typically processes a large number of rows, the high thread count on GPU requires the work to be split up into smaller pieces. Our implementation assigns a single GPU thread to a single row. If the matrix has a sufficient number of rows, the GPU will be saturated. For example, on the RX 6900 that would be 81920 rows and 218112 rows on the L40. In opposite, if the number of rows, thus threads, is too small, the GPU will not be saturated and performance may not be ideal. However, we do not optimise for small matrices because cache blocking is only meaningful solution for data which does not fit in the cache.

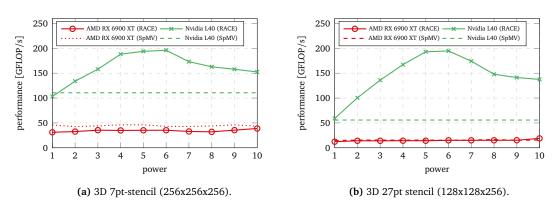

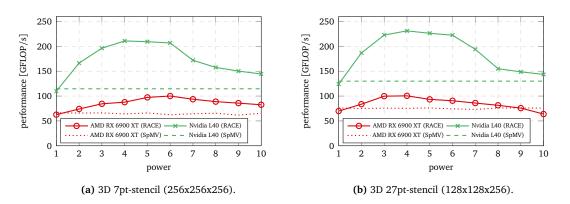

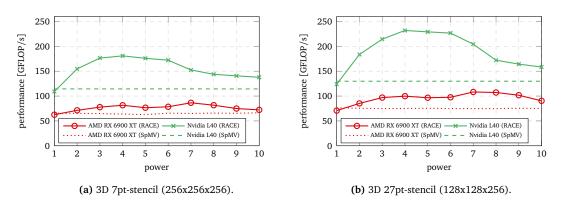

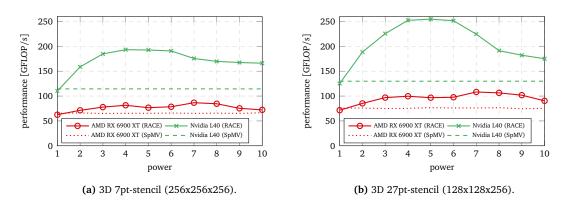

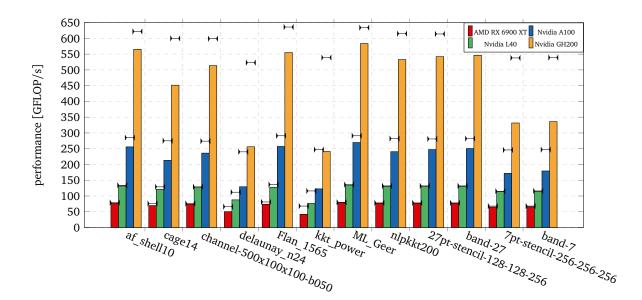

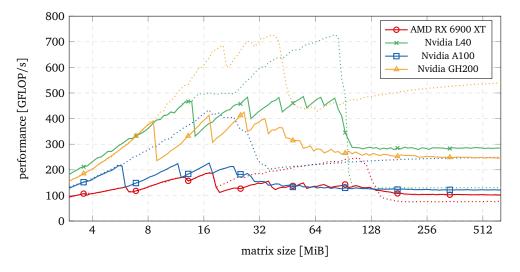

Figure 3.2 shows the performance of the naive GPU CRS kernel plotted over a range of powers. As mentioned previously, two stencil matrices are shown, and their MPK performance is compared between RACE and a regular SpMV based MPK. A very clear problem can be seen in the graphs with regard of performance on the RX 6900. Not only does the RX 6900 not benefit at all from RACE, it actually is worse than a traditional SpMV MPK calculation. Additionally, the figures are much lower than the approximated 85 GFLOP/s from (2.2) for regular SpMV. In contrast, the L40 becomes three times as fast as regular SpMV using RACE power calculation. However, no false conclusions should be made about speedup as long as the SpMV based MPK runs suboptimally. Once one considers that both cards exhibit only half the performance on the 27pt stencil with SpMV, it likely runs very poorly. Furthermore it is also far below the 144 GFLOP/s roofline.

These roofline figures ignore vector overhead and assume ideal caching behavior for col[i]. Accordingly the data intensity of 6 bytes per FLOP are approximate only. For very sparse matrices this can be 9 bytes or higher, but for the two stencils matrices it is in the range of approximately 6 to 7. Therefore estimation errors within this relative deviations are tolerable, but as shown the measured performance is much larger, especially on the RX 6900.

One common problem on GPUs for CRS kernels is load imbalance, as each thread may have to process a vastly different number of coefficients. This is not investigated, as stencil matrices do not have this problem since most rows are equally long. Both matrices under test are larger than one gigabyte to make sure they do not fit in the cache of the tested GPUs. RACE's cache size parameter is chosen with twice the size of the GPU's LLC. This is due to an implementation detail of RACE and is discussed in more detail in Section 4.4.2.5, but it also does not affect the standard SpMV results. As load imbalance is likely not the problem, the poor numbers must be caused by something else.

(b) CRS data order.

(a) CRS kernel (gpu-csr).

**Figure 3.1** – CRS on GPU example: The black arrow shows the order of the non-zeroes in memory.

Figure 3.2 – MPK-HIP: gpu-csr.

Unfortunately it is not possible to simply use vendor-optimized kernels, as they are typically limited to operate on entire matrices and not just slices of rows. A key element that we have discussed in Section 2.7 is the correct coalescing of memory accesses. In the following section we will explain why this is a huge problem with the CRS kernel.

#### **3.2.6** SELL-C- $\sigma$ (naive)

The CRS format does a reasonable job to keep the sparse matrix' memory footprint compact. As we briefly mentioned, good memory ordering is crucial to get good performance on GPUs. Unfortunately CRS is not ideal in this case. Good memory ordering means that all threads in a warp access the memory in a continuous block. Although potentially an extreme example, Figure 3.1 shows that the first column processed, which is accessed simultaneously, does not lie continuously in memory as the arrow indicates. When all threads fetch a coefficient from the first column simultaneously, the block accessed is not continuous and cannot be coalesced. Multiple matrix formats attempt to circumvent this, and most of them use a column-major layout instead of a row-major layout.

One of the challenges that a column-major layout has to solve is how to deal with uneven row lengths. All coefficients in neighbouring rows are supposed to be processed in parallel and the

```

void gpu_scs(val, col, chunkPtr, chunkLen, b, x) {

row

= blockIdx.x * blockDim.x + threadIdx.x;

2

= row / C;

= row % C;

3

chunk

idx

4

= chunkPtr[chunk];

5

ptr

rowlen = chunkLen[chunk];

6

= 0.0;

sum

for (i = 0; i < rowlen; i += 1) {

9

valColIdx = ptr + i * C + idx;

10

sum += val[valColIdx] * x[col[valColIdx]];

11

12

}

13

b[row] = sum;

14

15 }

```

(a) SELL-C- $\sigma$  kernel (gpu-scs-cm-trad).

(b) SELL-4-1 data order, correct memory coalescing for  $N_{\rm tpw} = 4$ , stripe shows padding.

**Figure 3.3** – SELL-*C*- $\sigma$  on GPU example: The black arrow shows the order of the non-zeroes in memory.

uneven memory accessed has to be fixed. This is usually solved by padding rows to be equally long, and a simple example of this is the ELLPACK format, which we covered previously. Although not with a stencil matrix, the ELLPACK format has the disadvantage that very few long rows can greatly increase matrix size. MPK-HIP implements an ELLPACK kernel, but we do not discuss its results, as we consider SELL-C- $\sigma$  to be a better compromise for arbitrary matrices.

With SELL-*C*- $\sigma$  the matrix is only ordered column-major for small chunks with *C* number of rows (see Figure 3.3b). If the chunk size *C* is chosen to fit the GPU's warp size of 32, memory access can be coalesced and thus better performance is expected. One of the reasons why SELL-*C*- $\sigma$  can reduce the amount of padding is that the rows are only padded to the maximum row size within a chunk. This can be improved further by increasing the sorting context  $\sigma$  since large rows will be grouped with other large rows. Unfortunately it is not possible to reorder rows in our case because this will conflict with RACE, as it already reorders the matrix during level formation. While this makes it impossible using SELL-*C*- $\sigma$  to its full extent, it is still better to use it with no sorting instead of using CRS or ELLPACK. Therefore MPK-HIP implements SELL-*C*- $\sigma$ , but only with  $\sigma = 1$ . This includes all results in this chapter and the final evaluation (see Chapter 4).

In Figure 3.3b the results for the SELL-*C*- $\sigma$  kernel can be seen. Compared to previous results in Figure 3.1, the graph for the RX 6900 is vastly different. The baseline performance with the SpMV 27pt kernel speeds up from 15 GFLOP/s to 75 GFLOP/s. This is already much closer to the 85 GFLOP/s roofline. Although not as high, the SpMV performance for the 7pt kernel also increases. It is an extreme example, but it shows very clearly why coalescing memory accesses is important to achieve good performance on GPU.

Because the performance of the L40 with CRS was already much better, its difference is not as large. For 27pt SpMV performance increases by at least a factor of two while the 7pt performance remains for the most part unchanged. The L40 already experienced speedup over SpMV with RACE with CRS, but in this measurement with SELL-C- $\sigma$  the peak performance is slightly higher while performing a lot better overall for non ideal powers. Overall, using SELL-C- $\sigma$  over CRS is a very clear decision. Unfortunately the RX 6900 does not profit from RACE as much as the L40, but more detailed explanations for this behavior can be found in Chapter 4.

With this higher base performance, one more effect is visible in the RX 6900 graph. SpMV performance is expected to be constant regardless of the power calculated, but the RX 6900 graph is not entirely flat. There is a peak-to-peak variation of about 5% for all different powers. The graph does not show that this 5% variation also occurs on a run to run basis with the same power. Consequently this can be attributed to measurement errors. It is unclear whether this is caused by

**Figure 3.4** – MPK-HIP: *gpu-scs-cm-trad* ( $C = 32, \sigma = 1$ ).

the GPU hardware or the driver stack, but due to HIP's novelty, we consider a driver problem to be a reasonable assumption. Since the L40 does not show this problem in this graph nor in any other graph that we present, we assume that the benchmark itself can be excluded as root cause.

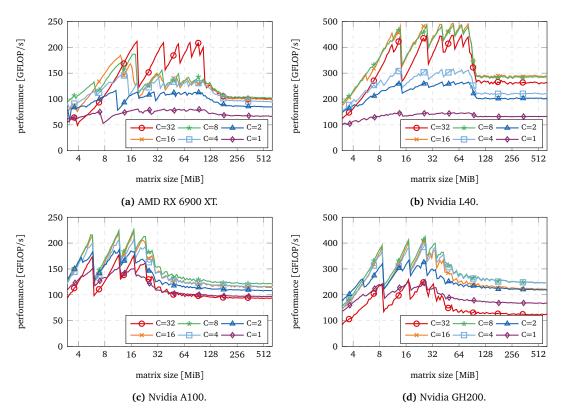

The 7pt stencil performance is overall lower compared to 27pt, but that is expected, as with fewer values per row cause more overhead per row. Exact explanations for these differences can be found later in Chapter 4. Yet there are still more options for optimization. During execution we observed for the RX 6900 and the 27pt matrix that each RACE kernel call would operate on ~47000 rows. In contrast, each classic SpMV kernel would operate on ~4200000 rows. The latter one easily saturates the RX 6900 with threads while the former one does not. We considered that this could have a negative impact on achievable memory bandwidth.

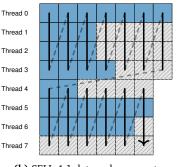

With the currently described SELL-*C*- $\sigma$  kernel, a single thread is assigned to each row like for CRS. In order to exclude the possibility of the GPU not being saturated properly, we opted to extend this SELL-*C*- $\sigma$  kernel to use more threads per row. This is covered in the next section.

#### 3.2.7 SELL-C- $\sigma$ (multi threaded)

In this section we show how to extend our previous SELL-*C*- $\sigma$  kernel to utilize multiple threads per row. Its main intention is to increase the total number of threads in order to saturate the GPU, which would not saturate otherwise. We will assume that the matrix benefits from that, even though there may be cases where using more threads may result in worse performance. For example, if the number of rows is already high enough to launch enough threads, this optimization is unnecessary and may even be counterproductive.

The simplest solution to use multiple threads per row is to first divide a row by the number of threads it is supposed to be processed by and let second each thread only multiply and add a subset of the row. The rows are then divided by a thread count which is a power of two, as this simplifies reduction. That way each row's result can be accumulated like a binary tree. Dividing by a power of two has the distinct disadvantage of more idling threads, as a row length may not necessarily be divisible by a power of two. This is a consciously accepted problem, as the only well performing solution would be to pad the matrices to the correct row length. However, padding the rows to a length of a power of two would increase storage requirements beyond SELL-*C*- $\sigma$ 's usual padding. In that case the additional bandwidth required could substantially decrease speedup.